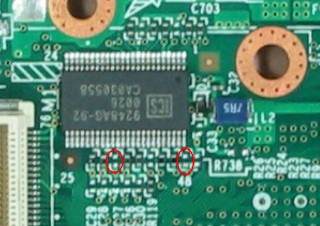

完動実機のメモリ実装個所。

#(サムネイルをクリックすると大きな画像が見れます。

#かなりでかい画像なので注意。

見たところ、DRAMとパスコン以外の追加実装品は無いように見える。

実際、DRAMを実装しただけでは認識しないと言う報告なので、別の理由があると思い調査すると、DRAM駆動するための CLK ラインが Bank

毎別ラインに分かれていることが判明。

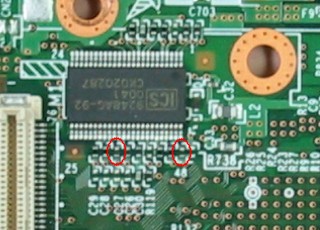

そこで、クロックジェネレータチップ周辺を調べて見た。

#(サムネイルをクリックすると大きな画像が見れます。

#かなりでかい画像なので注意。

このチップの各信号ラインの先を比較して見ると。。。。

なんだか、妖しい抜けパターンがジャンク基板にはある。。。(赤丸)

9248-92直下のチップ抵抗パターンは、9248-92の各種信号線に直結している。

左の赤丸は 9248-92 の 35pin (SDRAM1) からの信号、右の赤丸は 同45pin (REF2) からの信号となっている様子。

つまり、ジャンク基板の方は、この抵抗が抜けているために、DRAM Bank に クロックが供給されていないって言うことなのかな?

激しく妖しいなぁ〜〜〜〜〜〜〜〜〜。

ちなみに、チップ抵抗の実測値は 22Ω。

その後 (2002/06/19)

上記のとおり、35pin に直結している空きパターン (R24) を補完することで 128MB化 できるようです。

45pin への空きパターン (R5) については MKKさん所有の MB には実装済みだったそうなので、必要かもしれません。

実際にチャレンジを行った MKK さんがご自身のサイトで結果を公開されています。

すばらしい!!!